���W������e/ԭ�ӌӳ��e�~ǰ��w���о��Mչ

�����S������I��Ŀ��ٰlչ�����ڼ����·���������B���~��ĤҪ����Пoȱ�ݲ��Ҹ��ȵ����������Ľ�B�����û��W������e���g�cԭ�ӌӳ��e���g���e�~��Ĥ��ˇ���о����e�ǣ��C�����~-�u�ء�β-��ͪ�������������һ����h���ϩ���ȸ���~ǰ��w���о��F���c�lչڅ�ݣ������ˑ�������ǰ��w�M���~��Ĥ���e�ą��������Ƃ��~��Ĥ�Č�����ܡ����B�˱��n�}�M���~��Ĥ���e���о��Mչ��

�����S������Ҏģ�����·�İlչ�����b�ܶȲ������ʹ�ü����·���������ߴ粻��sС��оƬ�л��B�����L�Ⱥ͌Ӕ��������ӣ��������迹���ߣ� �������B���ľ��x�����pС��ʹ���g��ݳ��m�������M�ܼ����·���T���t�S�������ߴ�sС���pС�������以�B���t( RC ���t��R �ǻ��B���ٵ���裬C�Ǻͽ��|���P�����) ���}׃��Խ��Խͻ�������˽��ͻ��BRC ���t���������OӋ������Ҫ�������M�Ў����⣬�ڹ�ˇ������ø�������ʵĽ��ٲ������黥�B���ɞ��Ҫ��

������1998 ��IBM ��˾����Cu ���B�������ԁ�����Cu ������yAl �����µĻ��B������һֱ�Ǵ�Ҏģ�����·�о��ğ��c�������ڂ��y��Al���B��Cu���и��õČ����(20��rCu ������ʞ�1.67μΩ·cm��Al ������ʞ�2.65 μΩ·cm) ����Cu ����Al ���B������轵��37%����ʹ�����·( IC) ���ٶ���s4 �������⣬Cu �Ŀ���w���Ա�Al �߃ɂ����������~���B�܉Ͳ���RC ���t�������·���t�еı��أ�ʹIC �Ŀɿ����ܼ��ٶȵõ���ߣ����Cu ���J����һ�N���^����Ļ��B���ϡ�

��������ʹ�÷����x�ӿ��g��ˇ���gCu �Įa��]�l�Ե��Լ��~�����x�ӿ��g�ضȸߵ�ԭ��ĿǰCu���B�D�λ������p�Ƕ��ˇ(Damascene) ����ԓ��ˇҪ�����~ǰ�ڰ댧�w�Ĝϲۃ����Lһ�Ӿ����B�m���~�Ѿ��ӣ�Ŀǰ�ձ�ʹ���ſ؞R�似�g���e�~�Ѿ��ӡ��S�������·�ߴ�IJ���sС�����ôſ؞R�似�g�����e�Ѿ��~�ڱ����Լ������Է����y�ԝM��Ҫ����2012 �����ć��H�댧�w���g�lչҎ��( ITRS-2012 updated) ���贩��(Through-Silicon Via��TSV) 2014 ������_��10��1��2018 ���_��20 ��1���������������e( Physical Vapor Deposition��PVD) ���g���y������˸ߵ���ȹ贩���Ќ��F���������_�A���w�ʵ��~�Ѿ��ӳ��e��

�����c���������e��ȣ����W������e(Chemical Vapor Deposition��CVD) �����������e��Ĥ����ȸߣ��x����e���ܺü����e�ض������͵ȃ��c���V�������ڹ��ܱ�Ĥ���e��Ȼ�������~��ĤCVD���e���mȻ�����^�ߵ���Ȝϲ������^�ñ�Ĥ���w�ʣ����Ǯ���ȴ���һ��ֵ��( ������ȴ���10) ���䑪��Ҳ�ܵ����ơ�

����ԭ�ӌӳ��e( Atomic Layer Deposition��ALD) ���g��Ҳ�Q��ԭ�ӌ��������L(ALE) ���g����CVD����һ��ʽ���l���������o70 �������ֱ��20 ���oĩ�������������С�ͻ����F�Ć��}�������˂����Pע��ALD���g���Ѓɴ��c��һ�ǿ��Ծ��_���������e�ı�Ĥ��ȣ� ���������e�ı�Ĥ�������õľ������c�����ԡ����īI���������ALD���g������ȴ���35��1 �Ĝϲ�/ͨ���г��e���w�ʞ�100%���~��Ĥ��

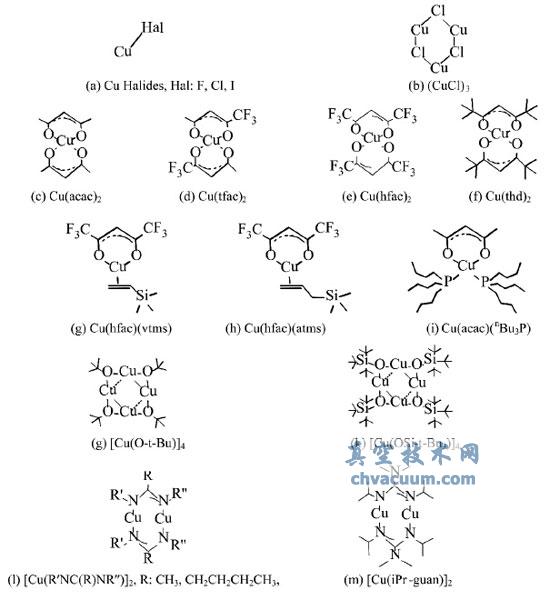

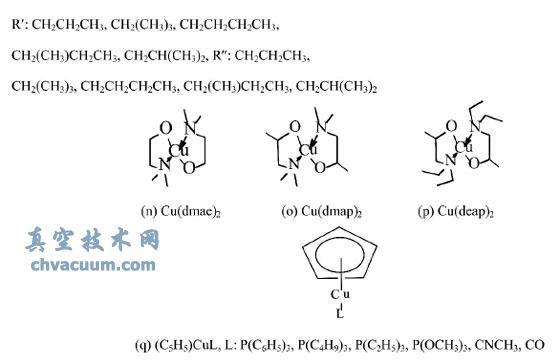

��������CVD�cALD���g���e���ܱ�Ĥ��Ҫ���]��������ǰ��w���x���m����CVD��ALD��ˇ��ǰ��w���M�����l���� �ٓ]�l�Ժã������^�ߵ�����������ھ������ߵğ᷀���ԣ����c����������������Ļ��ԣ��ܷ������a�����ڷ��x����Ŀ�˱�Ĥ�o�����ã������a�ɱ��ͣ������̘I�������w���~ǰ��w���ԣ����ϻַ�������Ҫ�������īI�������D1 ��ʾ�������c�~���B��Ԫ�طN��Ɍ��D1 �е�ǰ��w�֞��~-�u�ء��~-�����~-������-�~-�����~-̼�ǰ��w������������ǰ��w�M�зքe��B��

�D1 CVD/ALD�~ǰ��w

�����YՓ�cչ��

���������^ϵ�y�ؽ�B������CVD��ALD���~ǰ��w�������~-�u����~-̼��~ǰ��w�������≺�͡��c����߀ԭ���������Բ���e�ضȸ�᷀���Բ��ԭ�����ʮ����о��c�����^�٣��~-���ǰ��w���e��һ�r�~��β-��ͪ����������lչѸ�٣��~-���ǰ��w�����䱾���в�������Ԫ�ز����c�䷴�����Ըߵ�ԭ������Խ��Խ����Pע��������γ��e�������Ժá����ȸߡ�������܃����~��Ĥ�������x����m���~ǰ��w�c߀ԭ���⣬��ν�������e�ضȣ������ڼ{��������Ĥ����ϵõ��B�m�ı�ĤҲ���~��Ĥ���e���P�I���}������Ŀǰ�о����c֮һ�������x���w������t�����ڽ�Q�ˆ��}�������~��Ĥ���e�C�����о���Ŀǰ���e�\���H�и����~�t����V���|�V���Y�����������\�ö�N�\���ֶ���X �侀������V���E�Aƫ��ȼ��g���F�~��Ĥ���e���ھ������y����δ����һ�о����c��