��ͨ���߾��ȕr�g-�����D�Q��������

������B��һ�N����USB2.0�ӿڵĶ�ͨ���߾��ȕr�g-�����D�Q��( time-to-digital converter , TDC) ���OӋ�c���F�������NIM-LVPECL �ƽ�D�Q�·�����ٴ����D�Q�·������FPGA �Ĕ���̎�������P߉���ƵȆ�Ԫ�·���OӋ,���o����TDC �Ĝyԇ����ָ�ˡ��Y������, TDC ����С�r�g�ֱ��ʞ�403ps ,�y���r�g������0��420 us ,�y��“���r�g”< 13 ns��TDC �ɏV�������ڸ߾��ȵĕr�g�g���y���I��,�e�������w�Еr�g�|�V�x(time-of-flight mass spectrometer , TOF-MS) �Ĕ����ɼ�����

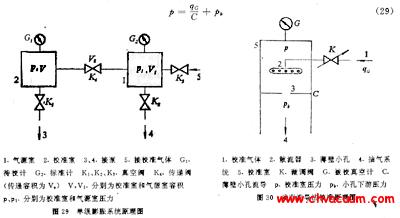

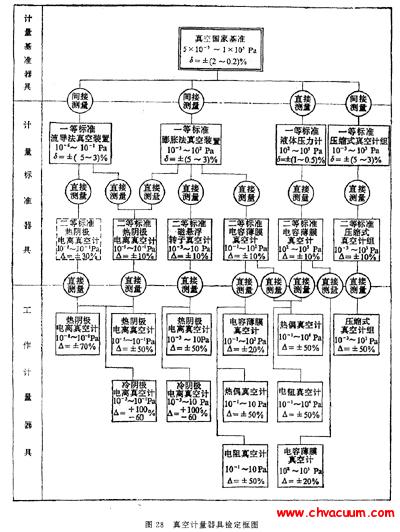

�������ܵĕr�g�y���ڿƌW�x��,ԭ�Ӻ˺����������о�,���ͨӍ,����y������|�ɷ֙z�y���I��������V���đ��á��w�Еr�g�|�V�x( time-of-dlight mass spect rometer , TOF-MS)������١��߾��ȡ��`���ȵķ����x��,��ͨ�^�y�����y�x���w�^һ�����x����Ҫ�ĕr�g��^�ֲ�ͬ�x�ӵ��|�ɱ�( m/z) ,�M���b�e�x�ӳɷ֡�TOF-MS ���١��߾��ȡ����`���ȵ����c�Q�����횾��иߕr�g�ֱ��ʺ��`���Ȕ����ɼ���̎���O��,Ŀǰ��õ��и���ģ�M�����D�Q��(analog-to-digital converter , ADC) �߾��ȕr�g�����D�Q��(time-to-digital converter ,TDC) ������TDC ��ԭ����ͨ�^ӛ�һ�Εr�g���x���}�_��̖�������|�l��̖( start)�ĵ��_�r�g�͔���,�^���ж����ӵķN��京����

�����҇����������w�Еr�g�|�V�x�ҕr�g�ֱ���С��1 ns �ĸ߾��ȕr�g�����D�Q�����о�����,Ŀǰ�H���ٔ�������W�������P�о�������������Ҹ���TDC �Ļ���ԭ��,�Y���L�ڏ��¸��ٔ����ɼ��ijɹ��аl���,������һ�Nͨ�����^���Ķ�ͨ���r�g�����D�Q��,����С�r�g�ֱ��ʞ�403 p s ,�y���r�g������0��420 us ,ϵ�y���r�g< 13 ns ,�����w�Еr�g�|�V�x���еõ����á�

1��TDC���w�Y���c��������ԭ��

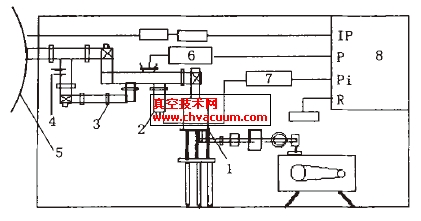

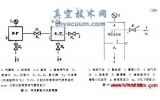

����TDC ϵ�y��Ҫ��ǰ����̖�{��ģ�K�����ٴ����D�Qģ�K�����ٕr犮a��ģ�K��FPGA ģ�K��USB �ӿ�ģ�K�Ȳ��ֽM��,ʾ�ڈD1 ����̖�{��ģ�K�ɔ�ģ�D�QоƬMAX5525 ���ٱ��^��ADCMP567 �M��;���ٴ����D�Qģ�K��Ҫ�ɴ����D�QоƬMAX3885 �M��;���ٕr犮a��ģ�K��AD ��˾�ĕr犮a��оƬAD951721 �M��;����̎��������ģ�K��XIL INX VIRTEX24 SX35FPGA �����P����·�M��;USB2. 0 ��ݔ������ģ�K��Cyp ress ��˾��CY7C68013 �����P����·�M�ɡ�

�D1 ��TDCӲ���Y���D

5���YՓ

���������w�Еr�g�|�V�x���đ��ñ���,�����һ�N���ڸ��ٴ����D�Qԭ���Ķ�ͨ���߾��ȕr�g-�����D�Q�����OӋ����,�����H�����c�{ԇ,���OӋ�_�����A�ڵ��OӋĿ��,�r�g�y��������0��420 us ,���H�yԇ��С�r�g�ֱ��ʞ�403 p s ,���Զ����á�Ŀǰ,ԓTDC �ё����ڏV�ݺ��ŷ����x������˾���w�Еr�g�|�V�x�������P�����,��Ӌ�\�ж���400 h ,�w�F���^�ߵĿɿ��ԡ��������c��ᘌ��z�y�ӑB����,��С�r�g�ֱ��ʺ��`���ȵ���Ҫ�����Mһ��������

�������x:���x�Ϻ���W�S����ʿ���߂���ʿ�͏V�ݺ��ŷ����x������˾��ճ����Tʿ�ڹ����нo��Ď�����

�����īI:

����[1] �����ӕ�,��С��,�n����,��. һ�N�r�g-�����D�QNIM ���������[J ] . ����ӌW�c̽�y���g,2008 ,28 (1) : 68270.

����[2 ] ������Դ,�����~,�r����. �߷ֱ��ʕr�g�����D�Q�·��PLD ���F[J] . �댧�w���g, 2006 , (6) :4522455.

����[3] ���Ρ���,������,�����. ����PCI �����ĸ߾��ܕr�g�g���y���x������[J] . ��Ӝy���c�x���W��,2006 , 20 (3) : 40241.

����[4 ] ��CHRISTIANSEN J , LJUSL IN C , MARCHIOROA. An intergrated 16 channel CMOS time to digital converter [ J ] . Nuclear Science Symp , 1993 ,6252629.

����[5] ���ˡ���. �r�g2�����D�Q���ڕr�g�g���`��y���еđ���[J ] . �Ӌ�y���g, 2004 , (1) :53256.

����[6] ��������,�����,���ɏ�. ���ڔ������t���ĸ߷ֱ���TDC ϵ�y[ J ] . �˼��g, 2005 , 28 ( 3 ) :1732175.

����[7 ] ��������,�S���\. �߾��ȕr�g�g���y�����g�c����[J ] . ���ČW�Mչ, 2006 ,24 (1) :1215.

����[8] ��MOTA M , CHRISTIANSEN J . A high2resolution time interpolator based on a delay locked loop and an RC delay line [J ] . IEEE Journal of SolidState Circuit s , 1999 ,34 (10) : 1 36021 366.

����[9] ��MOTA M. Design and characterization of CMOShighresolution time-to-digital converter [D] . Universidade Téchica de Lisboa Instituto SuperiorTéchico , 2000.

����[10] ���ߡ���,�S����,���L��,��. ����Z��Դ��ֱ����ʽ�w�Еr�g�|�V�x������[ J ] . �|�V�W��,2008 ,29 (4) :2092212.